### Marvell<sup>®</sup> PXA270M Processor

Specification Update

Doc. No. MV-S900957-00 Rev. I, PUBLIC RELEASE April 19, 2010

MOVING FORWARD FASTER®

#### **Document Conventions**

#### Note

Provides related information or information of special importance.

#### Caution

Indicates potential damage to hardware or software, or loss of data.

### Warning

Indicates a risk of personal injury.

#### Document Status

Doc Status: Rev H Public Release 4-19-10 Technical Publication: 0.xx

For more information, visit our website at: www.marvell.com

#### Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document.

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information.

Copyright © 2010. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas, Link Street, NetGX, PHYAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell. Ants, AnyVoltage, Discovery, DSP Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All other trademarks are the property of their respective owners.

Intel XScale® is a trademark or registered trademark of Intel Corporation and its subsidiaries in the United States and other countries.

## **Revision History**

| Revision Date  | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2010     | Rev I   | Added Errata 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| November 2009  | Rev H   | Added Specification Clarification S1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| May 2009       | Rev G   | Re-wrote the description for E94 for greater clarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| April 2009     | Rev F   | Added Errata E94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| February 2009  | Rev E   | Errata E16 fixed; Added Documentation Change D48; Updated Errata E59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| January 2009   | Rev D   | Added Documentation Change D47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| September 2007 | 012     | Added Errata 93<br>Added Documentation Change 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| September 2007 | 011     | Added Errata 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| July 2006      | 010     | Removed Specification Change 1, 2, 3, 4, 6, 7 and Documentation Change 1, 2, 4, 5, 6,<br>7, 8, 9, 10, 12, 14, 17, 18, 19, 20, 21, 23, 24, 25, 26, 28, 29, 30, 31, 32 because they<br>have been fixed in the <i>PXA27x Processor Family Developer's Manual</i> , January 2006,<br>Revision 003.<br>Added Errata 88, 89, 90, 91<br>Updated Errata 14, 61<br>Added Specification Change 13, 14, 15, 16<br>Updated Specification Change 11<br>Added Documentation Change 38, 39, 40, 41, 42, 43, 44, 45                                                                                                                                                                                                                   |

| December 2005  | 009     | Added Errata 83, 83, 84, 85, 86, 87<br>Updated Errata 21<br>Updated Specification Change 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| October 2005   | 008     | Added Documentation Change 34, 35, 36, 37         Added Errata 72, 73, 74, 75, 76, 77, 78, 79, 80, 81, 82         Added Specification Change 8, 9, 10, 11, 12         Added Documentation Change 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| July 2005      | 007     | Removed Specification Change 5 and Documentation Change 3, 11, 15, 16 because<br>they have been fixed in the <i>PXA27x Processor Family Electrical, Mechanical, and</i><br><i>Thermal Specification</i> , Revision 004 and <i>PXA270 Processor Family Electrical,</i><br><i>Mechanical, and Thermal Specification</i> , Revision 004.<br>Removed Documentation Change 13 because it has been fixed in the PXA27x<br>Processor Family Design Guide, Revision 002.<br>Added Errata 63, 64, 65, 66, 67, 68, 69, 70, 71<br>Added Specification Change 6, 7<br>Updated Specification Change 17, 18, 19, 20, 21<br>Updated Documentation Change 7<br>Added C0 and C5 columns in Table 4, "Summary of Specification Changes" |

Doc. No. MV-S900957-00 Rev. I

| Revision Date | Version | Description                                                                                                                                                                                                                                                              |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2005    | 006     | Updated PXA27x Processor Family Package Markings Figure 1<br>Updated Table 2<br>Updated Errata 37,60<br>Added Errata 61, 62<br>Updated Specification Change 1,2<br>Added Specification Change 5<br>Updated Documentation Change 6,11<br>Added Documentation Change 12-16 |

| February 2005 | 005     | Added Errata 60<br>Added Documentation Changes 9-11<br>Updated Documentation Changes 1-8                                                                                                                                                                                 |

| January 2005  | 004     | Added Errata 55, 56, 57, 58, 59<br>Updated Errata 17, 25, 26, 29, 30, 40, 42, 43, 45, 46<br>Added Documentation Change 1, 2, 4, 5, 6, 7, 8<br>Added Specification Change 1, 2, 3, 4                                                                                      |

| October 2004  | 003     | Added Errata 51, 52, 53, 54                                                                                                                                                                                                                                              |

| August 2004   | 002     | Added Errata 48, 49, 50<br>Added Documentation Changes 5 - 15                                                                                                                                                                                                            |

| April 2004    | 001     | Initial publication                                                                                                                                                                                                                                                      |

### **Preface**

This document contains updates to the specifications for the PXA27x Processor Family, listed in Table 1. This document is a compilation of device and documentation errata, specification clarifications, and specification changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, and tools.

Marvell Corporation has endeavored to include all documented errata in the consolidation process. However, Marvell makes no representations or warranties concerning the completeness of the *PXA27x Processor Family Specification Update*.

Information types defined in Nomenclature are consolidated into the *PXA27x Processor Family Specification Update* and are no longer published in other documents.

This document might also contain information that was not previously published.

## **Affected and Related Documents**

Table 1 lists the documents affected by and related to this errata update.

Contact a Marvell representative to obtain the latest revisions of these documents.

#### Table 1. Affected Documents / Related Documents

| Title                                                                     |

|---------------------------------------------------------------------------|

| PXA27x Processor Family Developer's Manual                                |

| PXA27x Processor Family Design Guide                                      |

| PXA27x Processor Family Electrical, Mechanical, and Thermal Specification |

| PXA270 Processor Family Electrical, Mechanical, and Thermal Specification |

### **Nomenclature**

**Errata** are design defects or errors. These errata might cause behavior of the PXA27x Processor Family to deviate from published specifications. Hardware and software designed to be used with any given processor stepping must assume that all errata documented for that stepping are present on all devices unless otherwise noted.

**Documentation changes** include typos, errors, and omissions from the current published specifications. These changes will be incorporated in the next release of the document.

**Specification clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the document.

**Specification changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the document.

**Note:** Errata remain in the specification update throughout the product's life cycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and made available upon request. Specification changes, specification clarifications, and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (data sheets, manuals, and so forth).

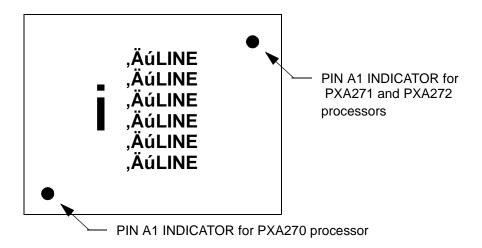

# **PXA27x Processor Family Package** Markings

The following figure depicts the location, on specific PXA27x Processor Family packages, where the actual markings are located.

Table 2 summarizes the processor packages.

*Note:* This table is for example only. It must not be used to determine final production offerings.

Table 2. Processor Package Summary

| Product                    | PXA270                                      | PXA270       | PXA271       | PXA272       |

|----------------------------|---------------------------------------------|--------------|--------------|--------------|

| Discrete / MCP             | Discrete                                    | Discrete MCP |              | MCP          |

| Package                    | 13x13 VFBGA                                 | 23x23 PBGA   | 14x14 FSCSP  | 14x14 FSCSP  |

| Flash                      | 0 Mb                                        | 0 Mb         | 1x 256L Tyax | 2x 256L Tyax |

| SDRAM                      | 0 Mb                                        | 0 Mb         | 1x 256 Mb    | 0 Mb         |

| Maximum Frequency          | Maximum Frequency 624 MHz 5                 |              | 416 MHz      | 520 MHz      |

| Lead / Lead-Free Both Both |                                             | Both         | Leaded       | Both         |

| Temp Range                 | Commercial Commercial / Extended Commercial |              | Commercial   |              |

| Stepping                   | C5                                          | C5 C5        |              | C5           |

# Summary of Changes

The following tables summarize the errata, specification changes, specification clarifications, and documentation changes that apply to the PXA27x Processor Family. Marvell might fix some of the errata in a future stepping of the component and account for the other outstanding issues through documentation or specification changes as noted. These tables use the following notations:

| Notation                 | Meaning                                                                                                             |

|--------------------------|---------------------------------------------------------------------------------------------------------------------|

| х                        | This erratum exists in the stepping indicated. Specification change or clarification that applies to this stepping. |

| (No mark) or (Blank Box) | This erratum is fixed in the listed stepping, or the specification change does not apply to the listed stepping.    |

| Plan Fix                 | This erratum might be fixed in a future stepping of the product.                                                    |

| Fixed                    | This erratum has been previously fixed.                                                                             |

| No Fix                   | There are no plans to fix this erratum.                                                                             |

| Doc                      | Marvell plans to update the appropriate documentation in a future revision.                                         |

| No Bug                   | This erratum has been determined to be a false erratum.                                                             |

| Shaded                   | This item is either new or modified from the previous version of the document.                                      |

### Table 3. Summary of Errata (Sheet 1 of 5)

| References |                                                                                                                                                     |      |   |   | PXA270M<br>A2 | Status |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|---------------|--------|

| Number     | Title                                                                                                                                               | Page |   |   |               |        |

| 1          | "CORE: IFU misses an external abort when a lock command is outstanding."                                                                            | 16   | Х | Х | Х             | No Fix |

| 2          | "CORE: Aborted store that hits D-cache might mark write-back data as dirty."                                                                        | 16   | Х | Х | Х             | No Fix |

| 3          | "CORE: Performance monitor unit counts, using performance monitoring event<br>number 0x1, can be incremented erroneously by unrelated core events." | 17   | х | х | х             | No Fix |

| 4          | "CORE: In SDS mode, back-to-back memory operations where the first instruction aborts might hang."                                                  | 17   | х | х | х             | No Fix |

| 5          | "CORE: Lock aborts resulting from I-cache or I-TLB lock operations are not presented properly on the trace interface."                              | 18   | х | х | х             | No Fix |

| 6          | "CORE: CP15 ID register accesses with opcode2 > 0b001 return unpredictable values."                                                                 | 18   | х | х | х             | No Fix |

| 7          | "CORE: Disabling and re-enabling the MMU can hang the core or cause it to execute the wrong code."                                                  | 18   | х | х | х             | No Fix |

| 8          | "CORE: JTAG parallel register updates require an extra TCK rising edge."                                                                            | 19   | Х | Х | Х             | No Fix |

| 9          | "MMC: SPI mode – if card is deselected, PROG_DONE will not be set."                                                                                 | 19   | Х | Х | Х             | No Fix |

| 10         | "MEMC: No MRS command is given when exiting from alternate bus master mode when SA-1111 address muxing mode is enabled."                            | 19   | х | х | Х             | No Fix |

| 11         | "KBD: Extra keypad matrix interrupt in IMKP mode."                                                                                                  | 20   | Х | Х | Х             | No Fix |

#### Table 3. Summary of Errata (Sheet 2 of 5)

| References |                                                                                                                                                                    |      |   |   | PXA270M<br>A2 | Status |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|---------------|--------|

| Number     | Title                                                                                                                                                              | Page |   |   |               |        |

| 12         | "USBH: USBH register UHCRHPSx[CCS] bit set incorrectly after power on"                                                                                             | 20   | Х | Х | Х             | No Fix |

| 13         | "AC97: Command-done bit remains set after an AC97 cold reset."                                                                                                     | 20   | Х | Х | Х             | No Fix |

| 14         | "POWER MANAGER: Fast ramp rates on voltage pins can cause high current consumption."                                                                               | 21   | х | х | х             | No Fix |

| 15         | "LCD: Reconfiguring the LCD controller retains the previous PPL value for the first line."                                                                         | 22   | х | х | х             | No Fix |

| 16         | "LCD: Overlay1 is not enabled intermittently after re-enabling LCD."                                                                                               | Х    |   |   | Fixed         |        |

| 17         | "POWER MANAGER: Processor ignores BATT/VCC faults while exiting sleep mode."                                                                                       | 23   | х | х | х             | No Fix |

| 18         | "KBD: Keyboard Edge-Detect Status Register Incorrect After Standby Mode Wakeup."                                                                                   | 23   | х | х | х             | No Fix |

| 19         | "UART: Character Timeout interrupt remains set under certain software conditions"                                                                                  | 24   | х | х | х             | No Fix |

| 20         | "LCD: LCD not enabling in dual panel mode."                                                                                                                        | 24   | Х | Х | Х             | No Fix |

| 21         | "UDC: UDC does not correctly support alternate interfaces."                                                                                                        | 25   | Х | Х | Х             | No Fix |

| 22         | "ICP: Receiver Aborts randomly occur prematurely and without End of frame/Error in FIFO interrupt"                                                                 | 26   | х | х | Х             | No Fix |

| 23         | "SSP: OSTimer counter increments incorrectly for SSP Frames in Network mode"                                                                                       | 26   | Х | Х | Х             | No Fix |

| 24         | "LCD: Enabling Overlay 2 for YUV420 hangs LCD controller."                                                                                                         | 26   | Х |   |               | Fixed  |

| 25         | "USBOTG: Unable to measure duration of Single-Ended Zero (SE0) for Session Request Protocol (SRP)"                                                                 | 28   | х |   |               | Fixed  |

| 26         | "MEMC: Write/Read to/from SDRAM can collide with alternate bus master mode when MDREFR:ALTREFB is set."                                                            | х    | х | Х | No Fix        |        |

| 27         | "POWER MANAGER: Core hangs during voltage change when there are<br>outstanding transactions on the bus"                                                            | х    | х | х | No Fix        |        |

| 28         | "MMC: MMC unit in SPI mode always waits a minimum of 1 Ncx cycles, even<br>though the MMC spec dictates that SPI mode CMD9 can have a minimum of 0<br>Ncx cycles." |      |   |   |               | Fixed  |

| 29         | "SD: SD Controller in SPI mode not receiving data response for CMD9 and CMD10 from some SD Cards"                                                                  | 31   | х |   |               | Fixed  |

| 30         | "MEMC: SDRAM Refresh Commands are issued too often during a VLIO access while BREQ is asserted."                                                                   | 31   | х | х | х             | No Fix |

| 31         | "INTERRUPT CONTROLLER: Unexpected exception vector when ICCR[DIM]=0 and ICMR=0."                                                                                   | 31   | х | х | х             | No Fix |

| 32         | "SSP: TXD line does not tristate when SSP is Slave to Frame"                                                                                                       | 32   | Х | Х | Х             | No Fix |

| 33         | "POWER MANAGER: Simultaneous BATT and VDD faults results in going to DeepSleep mode twice."                                                                        | 33   | х | х | х             | No Fix |

| 34         | "CORE: Non-branch instruction in vector table may execute twice after a thumb mode exception"                                                                      | 33   | х | х | х             | No Fix |

| 35         | "UART: UART does not correctly indicate a Framing Error Interrupt in DMA mode."                                                                                    | 33   | Х | Х | Х             | No Fix |

| 36         | "CLOCKS: System Hangs when enabling RUN/TURBO switching at 520 MHz"                                                                                                | 34   | Х | Х | Х             | No Fix |

| 37         | "CLOCKS: System Hangs when enabling HalfTurbo Switching"                                                                                                           | 35   | Х | Х | Х             | No Fix |

### Table 3. Summary of Errata (Sheet 3 of 5)

|        | References                                                                                                                                                  |      |   |   | PXA270M<br>A2 | Status |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|---------------|--------|

| Number | Title                                                                                                                                                       | Page |   |   |               |        |

| 38     | "MEMC: Memory Controller hangs when entering Self Refresh Mode."                                                                                            | 35   | Х | Х | Х             | No Fix |

| 39     | "SDIO: SDIO Devices Not Working at 19.5 Mbps"                                                                                                               | 36   | Х |   |               | Fixed  |

| 40     | "AC97: Command Done bit is never set when data is written in slot12"                                                                                        | 36   | Х | Х | Х             | No Fix |

| 41     | "SD/MMC: SD/MMC controller CRC errors with some SD/MMC cards"                                                                                               | 37   | Х |   |               | Fixed  |

| 42     | "USBH: There is no Individual Power Sense Polarity bit for each Host Port. The<br>Power Sense Polarity bit controls the polarity for all three Host Ports." | 37   | х |   |               | Fixed  |

| 43     | "KBD: Keypress wakeup from Standby mode is not reliable"                                                                                                    | 38   | Х | Х | Х             | No Fix |

| 44     | "USBH: USB Host Port 3 in Transceiverless Mode may not work correctly with an external device."                                                             | 38   | х |   |               | Fixed  |

| 45     | "SD/MMC: SPI mode commands fail even on cards that are compatible with SPI spec 1.0"                                                                        | 38   | х |   |               | Fixed  |

| 46     | "CLOCKS AND POWER: PWM Clock Enables do not work as specified"                                                                                              | 39   | Х | Х | Х             | No Fix |

| 47     | "ICP: Occasionally EIF, EOF and CRC interrupt are missed when a CRC error is received"                                                                      | 39   | х | х | х             | No Fix |

| 48     | "POWER MANAGER: Batt Fault does not always re-enable GPIO 0 and GPIO 1 as wake-up sources."                                                                 | 40   | х | х | х             | No Fix |

| 49     | "POWER MANAGER: The processor does not exit from sleep/deep-sleep mode."                                                                                    | 40   | Х |   |               | Fixed  |

| 50     | "SDIO: CMD53 multiple-block data transfer with block count set to 0 not<br>supported."                                                                      | 41   | х | х | х             | No Fix |

| 51     | "LCDC: Disable-done interrupt does not always occur."                                                                                                       | 41   | Х | Х | Х             | No Fix |

| 52     | "UDC: RCV can not be tied high during UDC transmission when using an external transceiver."                                                                 | 41   | х | х | х             | No Fix |

| 53     | "AC97: AC97 CAR[CAIP] bit field can be incorrectly set"                                                                                                     | 42   | Х | Х | Х             | No Fix |

| 54     | "SD/MMC: SD Command 56 Read Error"                                                                                                                          | 43   | Х |   |               | Fixed  |

| 55     | "AC97: AC97 Unit Incorrectly Receives An EOC"                                                                                                               | 43   | Х |   |               | Fixed  |

| 56     | "MMC: MMC Write CRC Response Error"                                                                                                                         | 44   |   | Х | Х             | No Fix |

| 57     | "USB: USB Host Port 3 Transceiverless Mode Restrictions"                                                                                                    | 45   |   | Х | Х             | No Fix |

| 58     | "MMC/SD/SDIO: Read Data Command May Hang The Controller"                                                                                                    | 45   | Х | Х | Х             | No Fix |

| 59     | "VCORE: Voltage Sensitivity at VVCCC(2,4) May Result in Undetermined System Behavior"                                                                       | 46   | х | х | х             | Fix    |

| 60     | "RTC: Stopwatch SWCR alarm inaccuracy"                                                                                                                      | 47   | Х | Х | Х             | No Fix |

| 61     | "MEMC: Memory Controller may hang while clearing MDREFR[K1DB2] or<br>MDREFR[K2DB2]"                                                                         | 48   | х | х | х             | No Fix |

| 62     | "POWER MANAGER: The processor can not execute the nBATT_FAULT or nVDD_FAULT xIDAE abort handler if a fault occurs while in sleep mode."                     | 49   | х | х | х             | No Fix |

| 63     | "POWER MANAGER: nBATT_FAULT and nVDD_FAULT during sleep mode do not prevent RTC wakeup."                                                                    | 49   | х | х | х             | No Fix |

| 64     | "POWER MANAGER: Voltage change coupled with power mode change causes<br>the processor to be unable to wake from sleep mode."                                | 50   | х | х | х             | No Fix |

| 65     | "SSP: GPIO[28] and GPIO[29] may not behave normally in SSP master mode."                                                                                    | 50   | Х | Х | Х             | No Fix |

| 66     | "SSP: SSP may hang when switching from slave mode to master mode."                                                                                          | 50   | Х | Х | Х             | No Fix |

#### Table 3. Summary of Errata (Sheet 4 of 5)

| References |                                                                                                                                                                                 |      |   |   | PXA270M<br>A2 | Status |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|---------------|--------|

| Number     | Title                                                                                                                                                                           | Page |   |   |               |        |

| 67         | "POWER MANAGER: Pins selected in the Keyboard Wake-Up Enable Register<br>(PKWR) may not cause the processor to wake up from sleep mode."                                        | 51   | х | х | х             | No Fix |

| 68         | "UHC: Exiting from sleep/deep sleep mode may cause unexpected USBH2 interrupt."                                                                                                 | х    | х | х | No Fix        |        |

| 69         | "UDC: USB OTG ID pin weak pullup draws 8 mA."                                                                                                                                   | 51   | Х | Х | Х             | No Fix |

| 70         | "CLOCKS: 48 MHz GPIO output stops during a USB suspend operation or if the USB client is not enabled."                                                                          | 52   | х |   |               | Fixed  |

| 71         | "POWER MANAGER: 8uS SYS_EN deassertion during watchdog reset."                                                                                                                  | 52   | Х | Х | Х             | No Fix |

| 72         | "VCC_USB must be 3.0 V or greater to pass USB signal quality compliance tests."                                                                                                 | 52   | Х | Х | Х             | No Fix |

| 73         | "MultiMediaCard Controller: MMCMD line is sensitive to capacitive loading."                                                                                                     | 53   |   | Х | Х             | No Fix |

| 74         | "UART: Baud rate may not be programmed correctly on back-to-back writes."                                                                                                       | 53   | Х | Х | Х             | No Fix |

| 75         | "AC97: PCM transmit FIFO and receive FIFO may not set the FIFO error status bits."                                                                                              | 53   | х | х | х             | No Fix |

| 76         | "UDC: Writing the UDCCSR0[OPC] bit during the status stage can corrupt the next transaction."                                                                                   | х    | х | х | No Fix        |        |

| 77         | "CI: Quick Capture Interface captures data before line valid signal occurs."                                                                                                    | 54   | Х | Х | Х             | No Fix |

| 78         | "MSL: Unexpected BBFREQ operation in 13M mode."                                                                                                                                 | 54   | Х | Х | Х             | No Fix |

| 79         | "KBD: Keypad interrupt missing after wakeup from Standby mode."                                                                                                                 | 54   | Х | Х | Х             | No Fix |

| 80         | "CLOCKS MANAGER: Possible DMA errors when exiting 13M mode to a<br>frequency where the memory controller clock (CLK_MEM) frequency does not<br>equal the system bus frequency." | х    | x | х | No Fix        |        |

| 81         | "GPIO: GPIO glitch during power up"                                                                                                                                             | 55   | Х | Х | Х             | No Fix |

| 82         | "I <sup>2</sup> C: I <sup>2</sup> C may hang if an external device holds SCL low without first deasserting SDA."                                                                | 55   | х | х | Х             | No Fix |

| 83         | "SSP: SSP1 generates a spurious Frame when switching from Frame Slave to Frame Master."                                                                                         | 56   | х | х | х             | No Fix |

| 84         | "MEMC: Data abort on access to disabled SDRAM."                                                                                                                                 | 56   | Х | Х | Х             | No Fix |

| 85         | "UART: TX data corruption when filling an empty FIFO."                                                                                                                          | 56   | Х | Х | Х             | No Fix |

| 86         | "POWER MANAGER: GPIO83 wake-up is level-triggered, not edge-triggered."                                                                                                         | 58   | Х | Х | Х             | No Fix |

| 87         | "SD/MMC: Streaming write (command 20) and streaming read (command 11) transfer one block."                                                                                      | х    | х | х | No Fix        |        |

| 88         | "SDRAM read and write errors while modifying MDREFR[KxDB2] if DMA is running"                                                                                                   | х    | х | х | No Fix        |        |

| 89         | "Limitations on combining core voltage changes with core frequency changes"                                                                                                     | 60   | Х | Х | Х             | No Fix |

| 90         | "MMC controller sending first FIFO byte twice"                                                                                                                                  | 60   | Х | Х | Х             | No Fix |

| 91         | "UART: TX interrupt can be missed when running full duplex"                                                                                                                     | 60   | Х | Х | Х             | No Fix |

| 92         | Caches, TLB (Translation Lookaside Buffer), and BTB (Branch Target Buffer) may become corrupted in Standby mode                                                                 | 60   | х | x | Х             | No Fix |

#### Table 3. Summary of Errata (Sheet 5 of 5)

|        | References                                                                                         |      |   |   |   | Status |

|--------|----------------------------------------------------------------------------------------------------|------|---|---|---|--------|

| Number | Title                                                                                              | Page |   |   |   |        |

| 93     | USB Host Controller Registers are not reset to their default values after sleep/deep-sleep wakeup. | 61   | х | x | х | No Fix |

| 94     | "USB OTG over-current pin can cause erroneous shutdown in the USB Host."                           | 62   | Х | Х | Х | No Fix |

| 95     | "Rapid power cycling may cause a processor hang"                                                   | 62   | Х | Х | Х | No Fix |

### Table 4. Summary of Specification Changes

| Number | Title                                                                     | Page | CO | <b>C5</b> | Status |

|--------|---------------------------------------------------------------------------|------|----|-----------|--------|

| 8      | "Extended Input DC operating conditions for USB interfaces"               | 63   | Х  | Х         | Doc    |

| 9      | "32.768-kHz crystal load capacitance specification updated"               | 64   | Х  | Х         | Doc    |

| 10     | "SDRAM 3.3 V Interface AC Timing Specification Updated"                   | 64   | Х  | Х         | Doc    |

| 11     | "Synchronous Flash AC Timing Specification Updated"                       | 66   | Х  | Х         | Doc    |

| 12     | "Quick Capture Interface AC Timing Added"                                 | 68   | Х  | Х         | Doc    |

| 13     | "SD/MMC: Remove section 15.8.4.5 "Stop Data Transmission, Randomly""      | 69   | Х  | Х         | Doc    |

| 14     | "32.768-kHz crystal equivalent series resistance requirements correction" | 69   | Х  | Х         | Doc    |

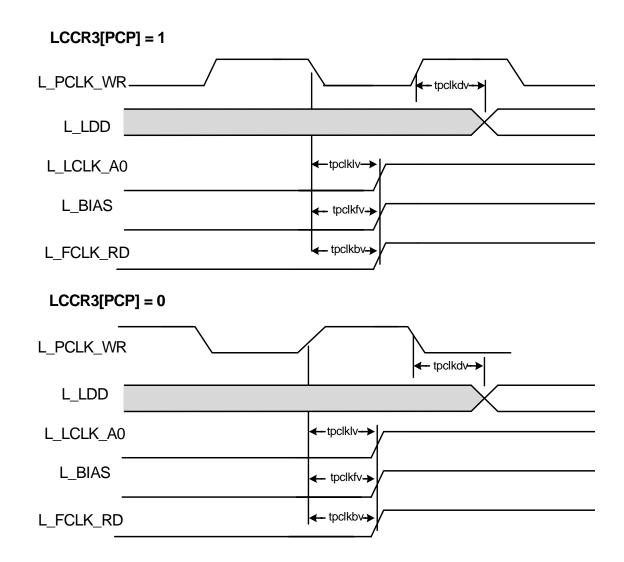

| 15     | "LCD controller timing specification updated"                             | 69   | Х  | Х         | Doc    |

| 16     | "PXA27x package information updated"                                      | 71   | Х  | Х         | Doc    |

### **Table 5. Summary of Specification Clarifications**

| Number | Document Revision         | Page | Status | Specification Clarifications                                                      |

|--------|---------------------------|------|--------|-----------------------------------------------------------------------------------|

| S1     | Spec Update<br>S900957-00 | 74   | 1000   | I/O pin drive strengths and internal resistive<br>pullup/pulldown values may vary |

### Table 6. Summary of Documentation Changes (Sheet 1 of 2)

| Number | Document Revision              | Page | Status | Documentation Changes                                 |

|--------|--------------------------------|------|--------|-------------------------------------------------------|

| 22     | EMTS 28000304<br>EMTS 28000205 | 75   | Doc    | "SDRAM Timing Parameter tsdCL Description Correction" |

| 27     | EMTS 28000304<br>EMTS 28000205 | 75   | Doc    | "VLIO Timing Parameter tvlioDH Correction"            |

| 33     | EMTS 28000304<br>EMTS 28000205 | 76   | Doc    | "Derating Specifications Removed From EMTS"           |

| 34     | EMTS 28000205                  | 77   | Doc    | "Ball Diameter for 23x23mm Package Added"             |

| 35     | Developers Manual 2800003      | 77   | Doc    | "UART Maximum Baud Rate Clarification"                |

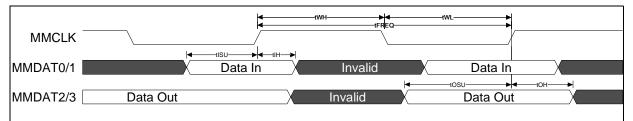

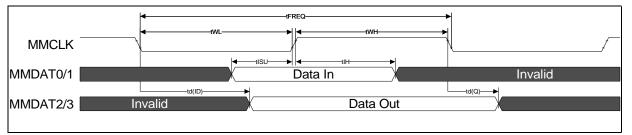

| 36     | EMTS 28000304<br>EMTS 28000205 | 77   | Doc    | "MMC/SD/SDIO AC Timings Added"                        |

| Number | Document Revision              | Page | Status | Documentation Changes                                                                                    |

|--------|--------------------------------|------|--------|----------------------------------------------------------------------------------------------------------|

| 37     | EMTS 28000205                  | 79   | Doc    | "Idle and Low-Power Mode Maximum Power-Consumption<br>Specifications Added"                              |

| 38     | Developers Manual 2800003      | 81   | Doc    | "MMC Read Time-Out Register (MMC_RDTO) Description Clari-<br>fication"                                   |

| 39     | EMTS 28000304<br>EMTS 28000205 | 81   | Doc    | "GPIO reset nRESET_OUT and GPIO<1> pulse width correction"                                               |

| 40     | EMTS 28000304<br>EMTS 28000205 | 83   | Doc    | "nBATT_FAULT and nRESET power-on reset description correction"                                           |

| 41     | EMTS 28000304<br>EMTS 28000205 | 83   | Doc    | "ROM timing parameters tromAVDVF and tromAVDVS correction"                                               |

| 42     | Developers Manual 2800003      | 84   | Doc    | "Keypad Interface external pull-down resistors specifications added"                                     |

| 43     | Developers Manual 2800003      | 85   | Doc    | "LCD controller output buffer strength description added"                                                |

| 44     | Developers Manual 2800003      | 86   | Doc    | "SD/MMC CMD12 no responses handling description added"                                                   |

| 45     | Developers Manual 2800003      | 86   | Doc    | "USB host Port 2 USBHPWR<2> and USBHPEN<2> clarifi-<br>cation"                                           |

| 46     | Developers Manual 2800003      | 86   | Doc    | COPROCESSOR: New CPU ID and JTAG ID Values                                                               |

| 47     | Specification Update           | 86   | Doc    | Incorrect Ball Diameter Listed in S16 for PXA27x Package<br>Information                                  |

| 48     | Specification Update           | 87   | Doc    | Removed last remaining mention (E16) of Memory Stick from<br>PXA270M Spec Update (not supported in 270M) |

### Table 6. Summary of Documentation Changes (Sheet 2 of 2)

### Errata

### E1. CORE: IFU misses an external abort when a lock command is outstanding.

Problem: A bus abort occurs on a code fetch while an I-TLB lock mcr is outstanding. The IFU fails to abort, instead executing the instruction returned on the aborting transaction. Parity errors are not affected. The bus abort might be due to either an ABORT pin assertion or a multi-bit ECC error on the core. On the core, the bus abort can occur as the result of a master abort, a target abort, or a single data phase disconnect on the system bus.

Implication: TBD

Workaround: Branch flush after every ITLB or I-cache lock.

Status: No Fix

### E2. CORE: Aborted store that hits D-cache might mark write-back data as dirty.

Problem: If an aborted store hits clean data in the data cache (data in an aligned four-word range that has not been modified from the core since it was last loaded in from memory or cleaned), the data in the array will not be modified (the store will be blocked), but the dirty bit will be set.

When that line is then aged out of the data cache or explicitly cleaned, the data in that four-word range will be evicted to external memory, even though it has never been changed. In normal operation, this will be nothing more than an extra store on the bus that writes the same data to memory as is already there.

This problem might be visible at the following boundary condition:

- 1. A cache line is loaded into the cache at address A

- 2. Another master externally modifies address A

- An Intel XScale<sup>®1</sup> core store instruction attempts to modify A, hits the cache, aborts because of MMU permissions, and is backed out the of cache. That line should not be marked "dirty", but because of this defect it will be.

- 4. The cache line at A then ages out or is explicitly cleaned. The original data from location A will be evicted to external memory, overwriting the data written by the external master.

This situation happens only if software is allowing an external master to modify memory that is write-back or write-allocate in the XScale page tables, and depending on the fact that the data is not dirty in the XScale cache to preclude the cached version from overwriting the external memory version. If there are any semaphores or any other handshaking to prevent collisions on shared memory, this should not be a problem.

Implication: TBD

<sup>1.</sup> Intel XScale is a trademark or registered trademark of Intel Corporation and its subsidiaries in the United States and other countries.

Workaround: For a shared memory region, mark it as write-through memory in the XScale page table to prevent the data from ever being written out as dirty, so the defect does not appear. Alternatively, ensure that any cached copy of the data in external memory is invalidated if an external agent modifies the external copy.

Status: No Fix

# E3. CORE: Performance monitor unit counts, using performance monitoring event number 0x1, can be incremented erroneously by unrelated core events.

- Problem: The performance monitor unit can be used to count cycles in which the I-cache cannot deliver an instruction. Performance monitoring event number 0x1 is used for this. According to EAS text, the only cycles counted should be those due to an I-cache miss or an I-TLB miss. The following unrelated events in the core also cause the corresponding count to increment when event number 0x1 is being monitored:

- Any architectural event (e.g. IRQ, data abort)

- mstr instructions that alter the CPSR control bits

- Some branch instructions, including indirect branches and those mis-predicted by the BTB

- CP15 mcr instructions to registers 7, 8, 9, or 10 which involve the I-cache or the I-TLB

Each of the items above might cause the performance monitoring count to increment several times. The resulting performance monitoring count might be higher than expected if the above items occur, but never lower. The performance monitor unit uses ic\_instValid\_qf2h. This signal asserts not just at the proper time, but also due to the events described above.

Implication: TBD

Workaround: There is no way to obtain the correct number of cycles stalled due to I-cache misses and I-TLB misses. One component of the unwanted noise may be filtered out: extra counts due to branch instructions mis-predicted by the BTB. The number of mispredicted branches can also be monitored using performance monitoring event 0x6 during the same time period as event 0x1. The mispredicted branch number can then be subtracted from the I-cache stall number generated by the performance monitor to get a value closer to the correct one. Depending on the nature of the code monitored, this workaround might have limited value.

Status: No Fix

### E4. CORE: In SDS mode, back-to-back memory operations where the first instruction aborts might hang.

Problem: If back-to-back memory operations occur in SDS (special debug state, used by ICE and debug vendors) and the first memory operation gets a precise data abort, the first memory operation is correctly cancelled and no abort occurs. However, depending on the timing, the second memory operation might not work correctly. The data cache might internally cancel the second operation, but the register file may have score-boarded registers for that second memory operation.

The effect is that the part might hang (due to a permanently scoreboarded register) or that a store operation might be cancelled incorrectly.

Implication: TBD

Copyright © 4/19/10 Marvell

| Workaround:                                                                       | In SDS, any memory operation that might cause a precise data abort should be followed by a write-buffer-drain operation. This operation precludes additional memory operations from being in the pipe when the abort occurs. Do not use load multiple/store                                                                                                                                     |  |  |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                   | multiple, which might cause precise data aborts.                                                                                                                                                                                                                                                                                                                                                |  |  |

| Status:                                                                           | No Fix                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| E5.                                                                               | CORE: Lock aborts resulting from I-cache or I-TLB lock operations are not presented properly on the trace interface.                                                                                                                                                                                                                                                                            |  |  |

| Problem:                                                                          | This problem affects only processors that use the core's trace interface. An I-cache or I-TLB lock operation that results in lock abort creates a unique internal pipeline signal timing that causes trouble on the trace interface, which results in the core reporting the event as if it came with the next instruction executed after the aborting lock instruction, the data abort vector. |  |  |

| Implication:                                                                      | TBD                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Workaround:                                                                       | None.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Status:                                                                           | No Fix                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| <b>E6</b> .                                                                       | CORE: CP15 ID register accesses with opcode2 > 0b001 return<br>unpredictable values.                                                                                                                                                                                                                                                                                                            |  |  |

| Problem:                                                                          | The XScale core does not implement CP15 ID codes registers other than the Main ID register (opcode2 = 0b000) and the Cache Type register (opcode2 = 0b001). If any of the unimplemented registers are accessed by software (for example, mrc p15, 0, r3, c15, c15, 2), the value of the Main ID register should be returned. Instead, an unpredictable value is returned.                       |  |  |

| Implication:                                                                      | TBD                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Workaround:                                                                       | None.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Status:                                                                           | No Fix                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| E7.                                                                               | CORE: Disabling and re-enabling the MMU can hang the core or cause it to execute the wrong code.                                                                                                                                                                                                                                                                                                |  |  |

| Problem:                                                                          | If the MMU is disabled via the CP15 control register after being enabled, certain timing cases can cause the processor to hang. In addition, re-enabling the MMU after disabling it can cause the processor to fetch and execute code from the wrong physical address. To avoid these issues, the code sequence below must be employed whenever disabling the MMU or re-enabling it afterwards. |  |  |

| Implication:                                                                      | TBD                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Workaround:                                                                       | round: The following code sequence must be used to disable and/or re-enable the MMU safely.<br>The alignment of the mcr instruction that disables or re-enables the MMU must be<br>controlled carefully, so that it lies in the first word of an instruction cache line:                                                                                                                        |  |  |

| ;//@ The following code sequence takes r0 as a parameter. The value of r0 will be |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| ;//@ written to th                                                                | e CP15 control register to either enable or disable the MMU.                                                                                                                                                                                                                                                                                                                                    |  |  |

| mcr p15                                                                           | , 0, r0, c10, c4, 1 ;// @ unlock I-TLB                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                         | mrc            | p15,                                                                                          | 0, r0, c2, c0, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ;//@ CPWAIT                                  |  |  |  |  |

|---------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

|                                                         | mov            | r0, r0                                                                                        | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |  |  |  |  |

|                                                         | sub            | pc, p                                                                                         | oc, #4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |  |  |  |  |

|                                                         | b              | After                                                                                         | Align                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ;//@ branch to aligned code                  |  |  |  |  |

|                                                         | ALIGN          | 32                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ;//@ align to 32 bytes                       |  |  |  |  |

| Afte                                                    | rAlign         |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |  |  |  |  |

|                                                         | mcr            | •                                                                                             | 0, r0, c1, c0, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ;//@ enable/disable MMU, caches              |  |  |  |  |

|                                                         | mrc            | •                                                                                             | 0, r0, c2, c0, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ;//@ CPWAIT                                  |  |  |  |  |

|                                                         | mov            | r0, r(                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |  |  |  |  |

|                                                         | sub pc, pc, #4 |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |  |  |  |  |

| Stat                                                    | tus:           |                                                                                               | No Fix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |  |  |  |  |

| <b>E</b> 8                                              | -              |                                                                                               | CORE: JTAG parallel register updates require an extra TCK rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |  |  |  |  |

| Problem:                                                |                |                                                                                               | The IEEE 1149.1 spec states that the effects of updating all parallel JTAG registers should be seen on the falling edge of TCK in the Update-DR state. The XScale core parallel JTAG registers incorrectly require an extra TCK rising edge to make the update visible. Therefore, operations like hold-reset, JTAG break, and vector traps require either an extra TCK cycle by going to run-test-idle or by cycling through the state machine again to trigger the expected hardware behavior. |                                              |  |  |  |  |

| Implication:                                            |                | n:                                                                                            | TBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              |  |  |  |  |